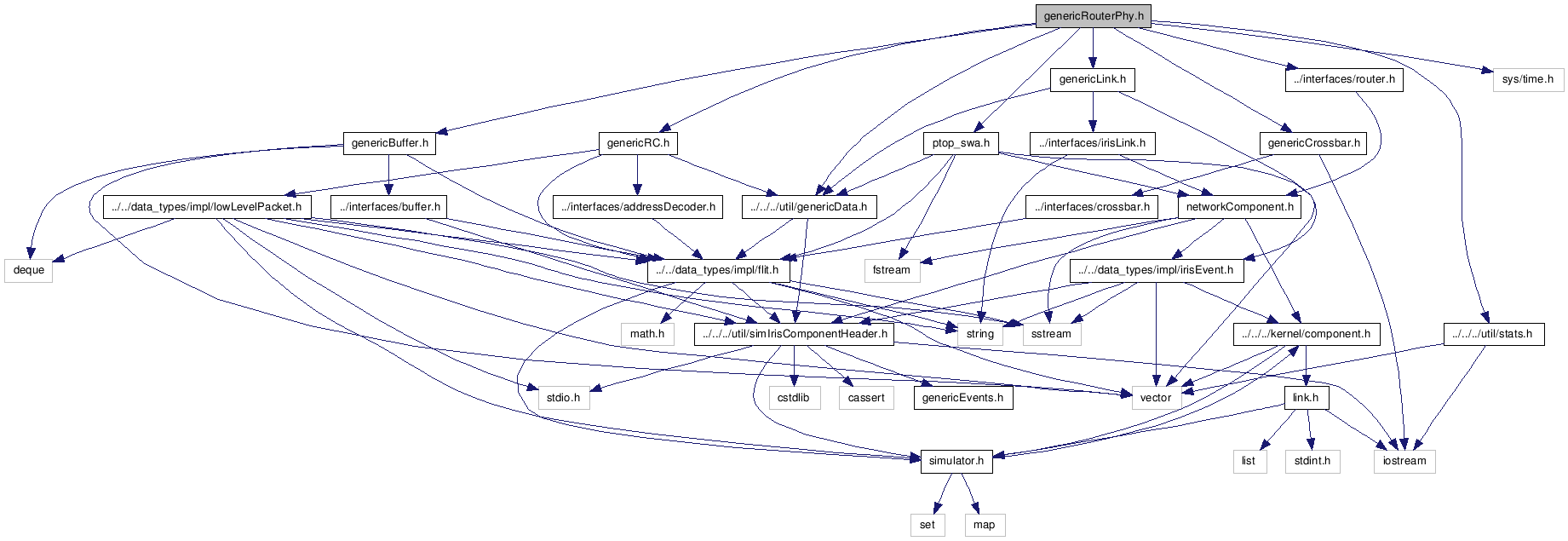

genericRouterPhy.h File Reference

#include "../interfaces/router.h"#include "genericBuffer.h"#include "genericRC.h"#include "ptop_swa.h"#include "genericCrossbar.h"#include "../../../util/genericData.h"#include "../../../util/stats.h"#include "genericLink.h"#include <sys/time.h>

Go to the source code of this file.

Classes | |

| class | GenericRouterPhy |

Variables | |

| uint | send_early_credit |

| uint | do_two_stage_router |

| uint | stat_print_level |

| IrisStats * | istat |

Variable Documentation

=====================================================================================

Filename: genericInterfaceNB.h

Description: Component that connects a PE to a router. This converts a HLP t flits and sends them out on the respective channel. It is non-blocking in the sense that flits are sent as long as there are credits for the downstream buffer available. In cases where you need to check send a new packet only if the next buffer is completely empty this wont work.

Version: 1.0 Created: 02/24/2010 02:04:22 PM Revision: none Compiler: gcc

Author: Mitchelle Rasquinha (), mitchelle.rasquinha@gatech.edu Company: Georgia Institute of Technology

=====================================================================================

Definition at line 33 of file config_params.h.

Definition at line 43 of file config_params.h.

=====================================================================================

Filename: genericRouterPhy.h

Description: This router is meant to work as a small low area low energy router. Does not understand virtual channels and thus does not hava a vca stage. Head flit: IB/RC->SA->ST body/tail flit: IB->ST (Good example for understanding simulation methodology of components and pseudo-components within iris)

Generral notes on router modelling: Router stages in a generic input buffered physical router model (BW->RC)->SA->ST->LT Buffer write(BW) Route Computation (RC) Virtual Channel Allocation (VCA) Switch Allocation (SA) Switch Traversal (ST) Link Traversal (LT)

Model Description in cycles: --------------------------- BW and RC stages happen in the same cycle in most models( BW pushes the flits into the input buffer and the RC unit. ) VCA: Allocate a virtual channel on the decoded output port(v virtual channels per port). SA: Pick one output port from n requesting input messages (0<n<pv) for the pxp crossbar ST: Move the flits across the crossbar and push it out on the link LT: This is not modelled within the router and is part of the link component.

Pipeline stages for the HEAD and BODY/TAIL are not the same. HEAD: (IB/RC)->VCA->SA->ST--->LT BODY/TAIL: IB/RC->SA->ST--->LT

When the tail goes thru ST it frees all resources. Flit level flow control is used for most routers. The credit is sent back in the ST stage when it is known for sure that the buffer will empty.

Version: 1.0 Created: 03/11/2010 08:56:06 PM Revision: none Compiler: gcc

Author: Mitchelle Rasquinha (), mitchelle.rasquinha@gatech.edu Company: Georgia Institute of Technology

=====================================================================================

Definition at line 39 of file config_params.h.

1.5.8

1.5.8