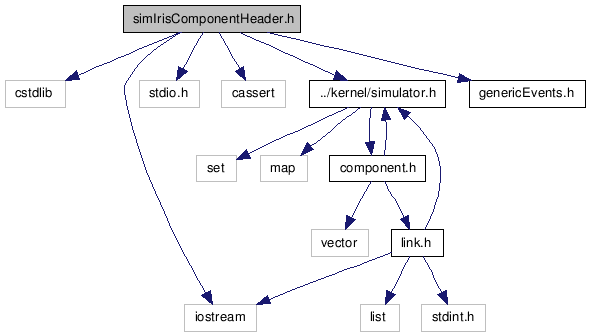

simIrisComponentHeader.h File Reference

#include <cstdlib>#include <iostream>#include <stdio.h>#include <cassert>#include "../kernel/simulator.h"#include "genericEvents.h"

Go to the source code of this file.

Defines | |

| #define | DEFAULT_ADDRESS 0 |

| #define | DEFAULT_CONVERT_PACKET_CYCLES 1 |

| #define | NO_DATA true |

| #define | FLIT_ID 9800 |

| #define | CREDIT_ID 9801 |

| #define | LOC cout << "\nTime:" << dec << Simulator::Now() <<" " << name << " " << address << " " << node_ip << " "; |

| #define | _DBG(fmt,...) LOC printf(fmt,__VA_ARGS__); |

| #define | _DBG_NOARG(fmt) LOC printf(fmt); |

| #define | LOC_log debug_log<< "\nTime:" << dec << Simulator::Now() <<" " << name << " " << address << " " << node_ip << " "; |

| #define | _DBG_log(fmt,...) LOC_log printf(fmt,__VA_ARGS__); |

Typedefs | |

| typedef unsigned long int | uniqueId |

| typedef unsigned long long int | simTime |

| typedef unsigned long long int | ullint |

| typedef unsigned int | uint |

Enumerations | |

| enum | message_class { INVALID_PKT, REQUEST_PKT, WRITE_REQ, RESPONSE_PKT, ONE_FLIT_REQ, CLUBBED_PKT, PRIORITY_REQ } |

| enum | virtual_network { VN0, VN1, VN2 } |

Variables | |

| const unsigned int | max_network_node_bits = 8 |

| const unsigned int | max_transaction_id_bits = 8 |

| const unsigned int | max_tail_length_bits = 8 |

| const unsigned int | max_control_bits = 8 |

| const unsigned int | max_pkt_cnt_bits = 3 |

| const unsigned int | head_and_tail_length = 80 |

Define Documentation

| #define _DBG | ( | fmt, | |||

| ... | ) | LOC printf(fmt,__VA_ARGS__); |

Definition at line 38 of file simIrisComponentHeader.h.

Referenced by GenericVcAllocator::clear_winner(), GenericRouterPhy::do_input_buffering(), RouterReqReply::do_switch_allocation(), GenericRouterPhy::do_switch_allocation(), RouterReqReply::do_switch_traversal(), GenericRouterPhy::do_switch_traversal(), GenericRouter4Stg::do_switch_traversal(), RouterReqReply::do_virtual_channel_allocation(), GenericInterfacePhy::handle_link_arrival(), GenericInterfaceNB::handle_link_arrival(), RouterVcMP::handle_link_arrival_event(), RouterReqReply::handle_link_arrival_event(), GenericRouterPhy::handle_link_arrival_event(), GenericRouter4Stg::handle_link_arrival_event(), GenericLink::handle_link_arrival_event(), McFrontEnd::handle_new_packet_event(), GenericTracePktGen::handle_new_packet_event(), GenericSink::handle_new_packet_event(), GenericRPG::handle_new_packet_event(), GenericPktGen::handle_new_packet_event(), GenericInterfacePhy::handle_new_packet_event(), GenericInterfaceNB::handle_new_packet_event(), GenericTracePktGen::handle_out_pull_event(), GenericPktGen::handle_out_pull_event(), McFrontEnd::handle_ready_event(), GenericTracePktGen::handle_ready_event(), GenericSink::handle_ready_event(), GenericPktGen::handle_ready_event(), GenericInterfacePhy::handle_ready_event(), GenericInterfaceNB::handle_ready_event(), GenericInterfacePhy::handle_tick_event(), GenericInterfaceNB::handle_tick_event(), RouterVcMP::process_event(), RouterReqReply::process_event(), GenericRouterPhy::process_event(), GenericRouter4Stg::process_event(), GenericRC::push(), GenericRC::route_negative_first(), GenericRC::route_north_last(), GenericRC::route_north_last_non_minimal(), GenericRC::route_odd_even(), GenericRC::route_west_first(), GenericRC::route_x_y(), and GenericRouterPhy::send_credit_back().

| #define _DBG_log | ( | fmt, | |||

| ... | ) | LOC_log printf(fmt,__VA_ARGS__); |

Definition at line 41 of file simIrisComponentHeader.h.

| #define _DBG_NOARG | ( | fmt | ) | LOC printf(fmt); |

Definition at line 39 of file simIrisComponentHeader.h.

Referenced by PToPSwitchArbiter::do_fcfs_arbitration(), PToPSwitchArbiter::do_priority_round_robin_arbitration(), PToPSwitchArbiterVcs::do_round_robin_arbitration(), PToPSwitchArbiter::do_round_robin_arbitration(), RouterVcMP::handle_detect_deadlock_event(), RouterReqReply::handle_detect_deadlock_event(), GenericRouter4Stg::handle_detect_deadlock_event(), GenericRPG::handle_ready_event(), GenericFlatMc::handle_ready_event(), GenericRouterPhy::handle_tick_event(), GenericRC::push(), and GenericPktGen::set_output_path().

| #define CREDIT_ID 9801 |

Definition at line 27 of file simIrisComponentHeader.h.

Referenced by GenericInterfacePhy::handle_link_arrival(), GenericInterfaceNB::handle_link_arrival(), RouterVcMP::handle_link_arrival_event(), RouterReqReply::handle_link_arrival_event(), GenericRouterPhy::handle_link_arrival_event(), GenericRouter4Stg::handle_link_arrival_event(), GenericInterfacePhy::handle_tick_event(), GenericInterfaceNB::handle_tick_event(), RouterVcMP::send_credit_back(), RouterReqReply::send_credit_back(), GenericRouterPhy::send_credit_back(), and GenericRouter4Stg::send_credit_back().

| #define DEFAULT_ADDRESS 0 |

Definition at line 23 of file simIrisComponentHeader.h.

| #define DEFAULT_CONVERT_PACKET_CYCLES 1 |

Definition at line 24 of file simIrisComponentHeader.h.

| #define FLIT_ID 9800 |

Definition at line 26 of file simIrisComponentHeader.h.

Referenced by RouterVcMP::do_switch_traversal(), RouterReqReply::do_switch_traversal(), GenericRouterPhy::do_switch_traversal(), GenericRouter4Stg::do_switch_traversal(), GenericInterfacePhy::handle_link_arrival(), GenericInterfaceNB::handle_link_arrival(), RouterVcMP::handle_link_arrival_event(), RouterReqReply::handle_link_arrival_event(), GenericRouterPhy::handle_link_arrival_event(), GenericRouter4Stg::handle_link_arrival_event(), GenericInterfacePhy::handle_tick_event(), and GenericInterfaceNB::handle_tick_event().

| #define LOC cout << "\nTime:" << dec << Simulator::Now() <<" " << name << " " << address << " " << node_ip << " "; |

Definition at line 37 of file simIrisComponentHeader.h.

| #define LOC_log debug_log<< "\nTime:" << dec << Simulator::Now() <<" " << name << " " << address << " " << node_ip << " "; |

Definition at line 40 of file simIrisComponentHeader.h.

| #define NO_DATA true |

Definition at line 25 of file simIrisComponentHeader.h.

Typedef Documentation

| typedef unsigned long long int simTime |

Definition at line 47 of file simIrisComponentHeader.h.

| typedef unsigned int uint |

Definition at line 49 of file simIrisComponentHeader.h.

| typedef unsigned long long int ullint |

Definition at line 48 of file simIrisComponentHeader.h.

| typedef unsigned long int uniqueId |

Definition at line 46 of file simIrisComponentHeader.h.

Enumeration Type Documentation

| enum message_class |

Definition at line 50 of file simIrisComponentHeader.h.

| enum virtual_network |

Variable Documentation

| const unsigned int head_and_tail_length = 80 |

Definition at line 59 of file simIrisComponentHeader.h.

| const unsigned int max_control_bits = 8 |

Definition at line 55 of file simIrisComponentHeader.h.

| const unsigned int max_network_node_bits = 8 |

Definition at line 52 of file simIrisComponentHeader.h.

Referenced by HeadFlit::populate_head_flit().

| const unsigned int max_pkt_cnt_bits = 3 |

Definition at line 58 of file simIrisComponentHeader.h.

Referenced by HeadFlit::populate_head_flit().

| const unsigned int max_tail_length_bits = 8 |

Definition at line 54 of file simIrisComponentHeader.h.

Referenced by TailFlit::populate_tail_flit().

| const unsigned int max_transaction_id_bits = 8 |

Definition at line 53 of file simIrisComponentHeader.h.

Referenced by HeadFlit::populate_head_flit().

1.5.8

1.5.8